The microchip model has been proven effective by companies such as Intel, AMD and Marvell, which design their own microchips and interconnects.

Then, the proposed chip based design requires several parts, such as product architecture, known good chip (KGD) and chip to chip interconnection.

On the latest 7Nm and 5nm nodes, costs and complexity soar.

This increases the cost of scrap.

This limits the adoption of small chip based methods to a small number of people.

Only a few large companies have the required in-house expertise and capabilities, most of which are proprietary.

According to Ahmad, here are some of the challenges: scrap costs: if a small chip fails in one or more final designs, the device may be scrapped.

KGD is a bare chip or small chip used in the design.

Small chips are challenging.

compression sleeve shin splints

compression sleeve shin splints

Thank you.

Traditionally, in order to develop complex IC products, suppliers have designed a chip that integrates all functions on the same chip.

“Just to give you a scale, the cost of making 5nm chips is about the same as that of making 10nm and 7Nm chips.

Testing: in order to minimize waste loss, the design needs more test coverage.

The open domain specific architecture (odsa) subproject is putting the finishing touches on similar technologies.

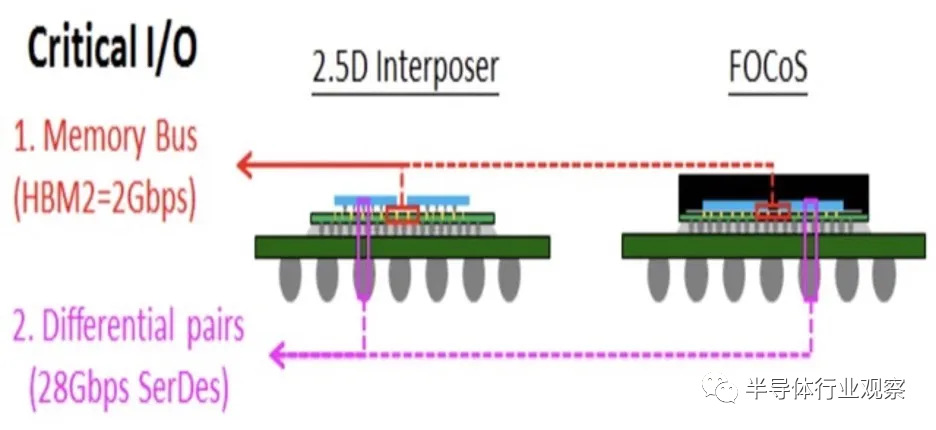

Chip to chip interconnection allows small chips to communicate with each other in design.

Now the chip based design industry is making it easier to access.

By developing or purchasing these components, chip customers can develop designs based on small chips, at least on paper.

Then, chip customers can choose any of these small chips and assemble them in an advanced package, resulting in a new and complex chip design as an alternative to system on chip (SOC).

To help customers here, odsa has released a cost analysis software tool, which includes developing spreadsheets of all possible components and costs involved in small chip based design.

It all depends on the specific application,” said mudasir Ahmad of Google.

Performance: moving signals from one chip to another may reduce the performance of the product.

The new microchip standard and the cost analysis tool used to determine the feasibility of a given microchip based design are two new and important parts.

(nodes refer to specific processes and their design rules.) “The cost of designing new silicon nodes is rising,” mudasir Ahmad, Google’s senior technology development engineer, said in a recent speech.

Using this method, packaging companies can have modular chips or small chip “menus” with different functions and process nodes in the library.

They also promise to develop complex chips faster and can be customized for specific markets and applications.

The team released a new open die to die interconnect specification that enables small chips to communicate with each other in packages.

“If you have different suppliers offering different parts and you put them all in one package, who is responsible for what? Who is responsible for failure?” Ahmad asked..

Source: the content is compiled from semiengineering by semiconductor industry watch (ID: icbank).

These efforts include: ASE, AMD, arm, Google, Intel, meta, Microsoft, Qualcomm, Samsung and TSMC formed a new small chip alliance.

But the biggest question is whether the design is feasible or cost-effective.

Then they can try to understand whether it makes sense to make small chips for specific applications.” Cost is not the only factor.

It also needs a sound manufacturing strategy.

Odsa has just released a new cost analysis tool to help determine whether a given chip based design is feasible.

“We need a model that can be used for each application to provide feedback.

The business model is another challenge.

This may be a major stumbling block that prevents risk adverse chip customers from considering small chips.

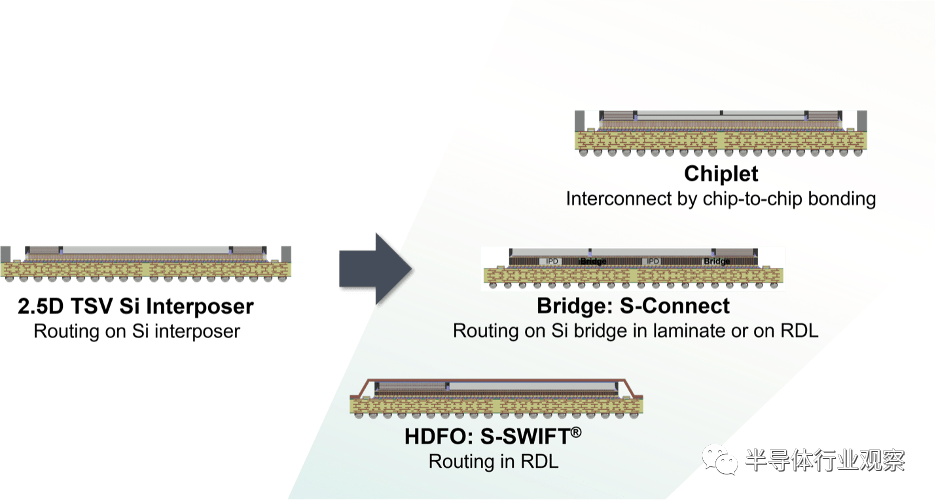

Several packaging companies are developing manufacturing technology to put small chip based designs into production.

“There is no general rule that you should always make small chips, or you shouldn’t.

Even so, building a model based on small chips requires several parts.

Usually, the first step in developing a design based on small chips is to define the product.

The packaging industry is trying to expand the adoption of small chips beyond several chip suppliers, laying the foundation for the next generation of 3D chip design and packaging.

Yield: packaging complexity may affect the overall yield.

Now, other companies in the industry are exploring small chips, mainly because expansion has become too difficult and expensive for many people, and the power and performance advantages of migrating to new nodes are shrinking.

Advanced packaging provides a cost-effective way to combine chips on different technology nodes, while small chips provide a solution to increase interconnect RC delay.

But like any new technology, chiplet integration is not simple.

It’s very expensive.” Although the traditional method is still an option for new design, small chips provide customers with another solution.

Together with other efforts, their goal is to move the small chip model forward, although there are still challenges and gaps in the technology.

Engineers must also consider the challenges of small chips.

At present, the design based on small chip is specially used for high-end products rather than daily design.

In each subsequent generation, the number of functions of each chip increases sharply.

[with the spreadsheet, chip customer] can enter data into it using a common framework.